KTH Computer Science and Communication

# No Hypervisor Is an Island: System-wide Isolation Guarantees for Low Level Code

OLIVER SCHWARZ

Doctoral Thesis Stockholm, Sweden 2016

TRITA-CSC-A 2016:22 ISSN 1653-5723 ISRN-KTH/CSC/A--16/22-SE ISBN 978-91-7729-104-6 KTH School of Computer Science and Communication SE-100 44 Stockholm SWEDEN

Akademisk avhandling som med tillstånd av Kungl Tekniska högskolan framlägges till offentlig granskning för avläggande av teknologie doktorsexamen i datalogi måndagen den 10 oktober 2016 klockan 14.00 i F3, Kungl Tekniska högskolan, Lindstedtsvägen 26, Stockholm.

SICS Swedish ICT SICS Dissertation Series 75 ISSN 1101-1335

Cover picture: The photograph that serves as background of the cover picture is courtesy of Lukáš Poláček.

© Oliver Schwarz, September 8, 2016

Tryck: Universitetsservice US AB

#### Abstract

The times when malware was mostly written by curious teenagers are long gone. Nowadays, threats come from criminals, competitors, and government agencies. Some of them are very skilled and very targeted in their attacks. At the same time, our devices – for instance mobile phones and TVs – have become more complex, connected, and open for the execution of third-party software. Operating systems should separate untrusted software from confidential data and critical services. But their vulnerabilities often allow malware to break the separation and isolation they are designed to provide. To strengthen protection of select assets, security research has started to create complementary machinery such as security hypervisors and separation kernels, whose sole task is separation and isolation. The reduced size of these solutions allows for thorough inspection, both manual and automated. In some cases, formal methods are applied to create mathematical proofs on the security of these systems.

The actual isolation solutions themselves are carefully analyzed and included software is often even verified on binary level. The role of other software and hardware for the overall system security has received less attention so far. The subject of this thesis is to shed light on these aspects, mainly on (i) unprivileged third-party code and its ability to influence security, (ii) peripheral devices with direct access to memory, and (iii) boot code and how we can selectively enable and disable isolation services without compromising security.

The six papers included in this thesis are both design and verification oriented, however, with an emphasis on the analysis of instruction set architectures. With the help of a theorem prover, we implemented various types of machinery for the automated information flow analysis of several processor architectures. We used these tools to make explicit which registers arbitrary and unprivileged software on ARM or MIPS platforms can access. The analysis is guaranteed to be both sound and accurate. To the best of our knowledge, we were the first to publish an automated analysis and verification of information flow properties for commodity instruction set architectures.

#### Sammanfattning

Förr skrevs skadlig mjukvara mest av nyfikna tonåringar. Idag är våra datorer under ständig hot från statliga organisationer, kriminella grupper, och kanske till och med våra affärskonkurrenter. Vissa besitter stor kompetens och kan utföra fokuserade attacker. Samtidigt har tekniken runtomkring oss (såsom mobiltelefoner och tv-apparater) blivit mer komplex, uppkopplad och öppen för att exekvera mjukvara från tredje part.

Operativsystem borde egentligen isolera känslig data och kritiska tjänster från mjukvara som inte är trovärdig. Men deras sårbarheter gör det oftast möjligt för skadlig mjukvara att ta sig förbi operativsystemens säkerhetsmekanismer. Detta har lett till utveckling av kompletterande verktyg vars enda funktion är att förbättra isolering av utvalda känsliga resurser. Speciella virtualiseringsmjukvaror och separationskärnor är exempel på sådana verktyg. Eftersom sådana lösningar kan utvecklas med relativt liten källkod, är det möjligt att analysera dem noggrant, både manuellt och automatiskt. I några fall används formella metoder för att generera matematiska bevis på att systemet är säkert.

Själva isoleringsmjukvaran är oftast utförligt verifierad, ibland till och med på assemblernivå. Dock så har andra komponenters påverkan på systemets säkerhet hittills fått mindre uppmärksamhet, både när det gäller hårdvara och annan mjukvara. Den här avhandlingen försöker belysa dessa aspekter, huvudsakligen (i) oprivilegierad kod från tredje part och hur den kan påverka säkerheten, (ii) periferienheter med direkt tillgång till minnet och (iii) startkoden, samt hur man kan aktivera och deaktivera isolationstjänster på ett säkert sätt utan att starta om systemet.

Avhandlingen är baserad på sex tidigare publikationer som handlar om både design- och verifikationsaspekter, men mest om säkerhetsanalys av instruktionsuppsättningar. Baserat på en teorembevisare har vi utvecklat olika verktyg för den automatiska informationsflödesanalysen av processorer. Vi har använt dessa verktyg för att tydliggöra vilka register oprivilegierad mjukvara har tillgång till på ARM- och MIPS-maskiner. Denna analys är garanterad att vara både korrekt och precis. Så vitt vi vet är vi de första som har publicerat en lösning för automatisk analys och bevis av informationsflödesegenskaper i standardinstruktionsuppsättningar.

### Acknowledgements

**No person is an island.** Especially no PhD student. In my case, they even gave me two lands that took care of me: the SICS-land and the KTH-land. Both came with one advisor each and – maybe without being aware of it – the two complemented each other pretty well.

My industrial advisor Christian Gehrmann understood to accompany my development with a supervision ever-aligned with the needs of my respective state. In the beginning he provided much initial guiding, followed by an increasing amount of trust, freedom, and responsibility – always on the right level, always *lagom mycket* to empower me. It is not granted for industrial PhD students to find that degree of freedom and time for research and studies that I received from Christian. He always cared about my progress and expressed his confidence in me. Thank you very much, Christian!

My gratitude also goes to my academic advisor Mads Dam. He always found time and patience to discuss technical details or writing matters. And this is still an understatement. As for technical details, it is more precise to say that Mads taught me to never stop discussing them until I really understand their gist. And as for writing, he went through uncountable iterations of proofreading with me. As much as I was striving towards his level of writing, I did not even come close and he still remains a role model in that respect. I also want to thank Mads for the freedom he granted me in my research questions and his confidence in the paths I have chosen towards their solutions.

Also, I want to thank Mads for creating a truly inspirational research environment. The PROSPER group at KTH was always a place to discuss, receive help, and get inspired. Working together with that group really was a pleasure. I want to thank their members, both my co-authors and the rest, namely Mads, Narges Khakpour, Hamed Nemati, Christoph Baumann, Andreas Lindner, Dilian Gurov, Musard Balliu, Andreas Lundblad, and Roberto Guanciale. Roberto, I am sorry that I do not know how to put this in a less stereotypical way, but you are a true role model, both as a scientist and a person.

Thanks go also to my co-authors and project partners at SICS, namely Christian, Viktor Do, Arash Vahidi, Heradon Douglas, and Jonas Haglund. Especially in the early days, you were my tour guides through the – back then for me inscrutable – jungle of low-level hardware and system software matters. Whenever I had a hardware or implementation question, you were the right address to look for the answer. I also want to thank the other members of the SEC lab, Rolf Blom, Rikard Höglund, Marco Tiloca, Nicolae Paladi, Antonis Michalas, Mudassar Aslam, Ludwig Seitz, our master students, and all our lab members in Lund, that I hopefully will get to know better in the future. Nicolae, thank you for proofreading so many of my papers – even though I use parentheses more often than your beloved dashes. Thank you also for all the interesting scientific discussions in your office. The rubber duck, the whiteboard pictures, and that strange little spinning tops created a pleasant and stimulating atmosphere for brainstorming. Marco, thank you for sharing your insights about the world, both in scientific and other respects. Mudassar, the same holds for you. It was great to share the office with you, share our views on being PhD students, and share our thoughts concerning the big questions of life.

Back in KTH-land, they also put me into an office, specifically, into the best office of the entire KTH. Thank you Benjamin Greschbach, Emma Enström, and Guillermo Rodríguez Cano for having kept it such a welcoming place that always encouraged people to drop by. Another place at the TCS-department that I never will forget is its kitchen. It was the home for countless interesting lunch discussions. Many people deserve thanks for this, but in particular Gunnar Kreitz, Lukáš Poláček, and Lukáš' mother. There are many more nice people at TCS. I like to thank them all for a nice working environment. I know these acknowledgements will be the most read part of the thesis and I know you are waiting for your names to be listed here. But I have been around for quite many years, so many people came and went, just too many to list all of you. But be sure that you are in my memories, nonetheless. The same goes for all the nice people at SICS. I cannot list you all, but I really enjoyed your company and help. Thanks to the old NETS lab, to the IT support, the receptionists, the administration, the Swedish teachers, the badminton partners, and all others. The heterogeneity of the people at SICS, of gender, age, profession, and origin creates the feeling of a big family that I really enjoyed.

Special thanks go to Mudassar, Benjamin, Nicolae, and Hamed. They have been there in the hard times that such an enterprise sometimes has. Thanks for comfort and encouragement and just being there as friends.

Thanks to all other people that I met on the way, all project partners, all interesting people I got to know at conferences and summer schools, and all anonymous reviewers that helped to improve my papers.

Thank you, Gerwin Klein, Mads, Karl Meinke, Nicolae, Christoph, Deborah Fauser, Rikard, Arash, and Jonas, for reviewing and commenting this thesis, be it a few lines or many many pages. I really appreciate your help.

I also want to thank all residents of Villa Leipzig, especially Barbro and Robert, but also the other students and further tenants, for providing me not only with accommodation, but also with a true home during my time as PhD student.

Many thanks go to my friends in Sweden, Germany, and all over the world. You have grounded me throughout these years. Thank you, Deborah for your patience and support. You allowed me to recharge on long working days. Vielen lieben Dank an meine Familie, insbesondere meine Eltern! Hättet ihr damals nicht die Besonnenheit gehabt, die offizielle Bildungsempfehlung zu ignorieren, wäre diese Doktorarbeit vermutlich nie zustande gekommen. Ihr fahrt durch halb Europa, um mir zu helfen, und seid auch sonst stets für mich da. Vielen Dank!

# Contents

| Co | Contents                                                                                                                                 |                                        |  |  |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| I  | Thesis                                                                                                                                   |                                        |  |  |  |

| A  | Acronyms                                                                                                                                 |                                        |  |  |  |

| 1  | Introduction                                                                                                                             | 5                                      |  |  |  |

| 2  | Background         2.1       Platform Security         2.2       Formal Verification         2.3       Verification of Platform Security | <b>9</b><br>9<br>16<br>25              |  |  |  |

| 3  | Contributions         3.1       Summary of Included Papers         3.2       Further Publications                                        | <b>35</b><br>36<br>40                  |  |  |  |

| 4  | Conclusions                                                                                                                              | 41                                     |  |  |  |

| 11 | Included Papers                                                                                                                          | 43                                     |  |  |  |

| Α  | Formal Verification of Information Flow Security for a Simple<br>ARM-Based Separation Kernel                                             | 45                                     |  |  |  |

|    | A.1 Introduction                                                                                                                         | 45<br>49<br>51<br>53<br>54<br>59<br>61 |  |  |  |

|    | A.8 Evaluation                                                                                                                           | 64                                     |  |  |  |

## CONTENTS

|              |                                                               |                                                           | 65<br>66 |  |  |  |

|--------------|---------------------------------------------------------------|-----------------------------------------------------------|----------|--|--|--|

| в            | Mac                                                           | chine Assisted Proof of ARMv7 Instruction Level Isolation |          |  |  |  |

|              | Pro                                                           | perties                                                   | 69       |  |  |  |

|              | B.1                                                           | Introduction                                              | 69       |  |  |  |

|              | B.2                                                           | The Formal Specification of ARM                           | 71       |  |  |  |

|              | B.3                                                           | Memory Management                                         | 73       |  |  |  |

|              | B.4                                                           | Security Properties                                       | 75       |  |  |  |

|              | B.5                                                           | The Logic Framework                                       | 78       |  |  |  |

|              | B.6                                                           | Implementation and Evaluation                             | 81       |  |  |  |

|              | B.7                                                           | Related Work                                              | 82       |  |  |  |

|              | B.8                                                           | Conclusion                                                | 83       |  |  |  |

| $\mathbf{C}$ | Aut                                                           | omatic Derivation of Platform Noninterference Properties  | 85       |  |  |  |

|              | C.1                                                           | Introduction                                              | 85       |  |  |  |

|              | C.2                                                           | Processor Models                                          | 87       |  |  |  |

|              | C.3                                                           | ISA Information Flow Analysis                             | 89       |  |  |  |

|              | C.4                                                           | Approach                                                  | 91       |  |  |  |

|              | C.5                                                           | Evaluation                                                | 96       |  |  |  |

|              | C.6                                                           |                                                           | 98       |  |  |  |

|              | C.7                                                           | I I I I I I I I I I I I I I I I I I I                     | .00      |  |  |  |

|              | C.8                                                           | Conclusions and Future Work                               | .01      |  |  |  |

| D            | Formal Verification of Secure User Mode Device Execution with |                                                           |          |  |  |  |

|              | $\mathbf{D}\mathbf{M}$                                        | A 1                                                       | 03       |  |  |  |

|              | D.1                                                           | Introduction                                              | .04      |  |  |  |

|              | D.2                                                           |                                                           | .05      |  |  |  |

|              | D.3                                                           |                                                           | .07      |  |  |  |

|              | D.4                                                           |                                                           | .08      |  |  |  |

|              | D.5                                                           |                                                           | .09      |  |  |  |

|              | D.6                                                           | Security Properties                                       |          |  |  |  |

|              | D.7                                                           | Implementation                                            |          |  |  |  |

|              | D.8                                                           | Conclusions                                               | .18      |  |  |  |

| $\mathbf{E}$ | Secu                                                          | uring DMA through Virtualization 1                        | 23       |  |  |  |

|              | E.1                                                           | Introduction                                              | .23      |  |  |  |

|              | E.2                                                           | Related Work                                              |          |  |  |  |

|              | E.3                                                           | Prerequisites                                             |          |  |  |  |

|              | E.4                                                           | Architecture and Hypervisor                               |          |  |  |  |

|              | E.5                                                           | DMA Virtualization                                        |          |  |  |  |

|              | E.6                                                           | Evaluation                                                |          |  |  |  |

|              | E.7                                                           | Formal Verification of a Simplified DMA Model             | .34      |  |  |  |

|              | E.8                                                           | Conclusions                                               | .35      |  |  |  |

| $\mathbf{F}$    | Affordable Separation on Embedded Platforms: |                                                       |    |  |  |  |  |  |

|-----------------|----------------------------------------------|-------------------------------------------------------|----|--|--|--|--|--|

|                 | Soft                                         | Reboot Enabled Virtualization on a Dual Mode System 1 | 37 |  |  |  |  |  |

|                 | F.1                                          | Introduction                                          | 37 |  |  |  |  |  |

|                 | F.2                                          | Hardware and Protocol                                 | 39 |  |  |  |  |  |

|                 | F.3                                          | Hypervisor                                            | 46 |  |  |  |  |  |

|                 | F.4                                          | Software Adaptions                                    | 46 |  |  |  |  |  |

|                 | F.5                                          | Evaluation                                            | 48 |  |  |  |  |  |

|                 | F.6                                          | Related Work                                          | 52 |  |  |  |  |  |

|                 | F.7                                          | Conclusion                                            | 54 |  |  |  |  |  |

| Reference Lists |                                              |                                                       |    |  |  |  |  |  |

| SI              | SICS Dissertation Series                     |                                                       |    |  |  |  |  |  |

| Bi              | Bibliography                                 |                                                       |    |  |  |  |  |  |

Part I Thesis

# Acronyms

This list contains the acronyms used in the first part of the thesis. The page numbers indicate primary occurrences.

**ARM ARM** ARM Architecture Reference Manual. 32

**BAP** the Binary Analysis Platform. 17

**BIOS** basic input/output system. 15

CC Common Criteria. 28

DMA direct memory access. 14

DMAC direct memory access controller. 39

EAL evaluation assurance level. 28

GPU graphics processing unit. 29

HDD hard disk drive. 15

IOMMU input/output memory management unit. 7, 15

**IPC** inter-process communication. 26

**ISA** instruction set architecture. 13

**MMU** memory management unit. 10

MPU memory protection unit. 10

NIC network interface controller. 15

**OS** operating system. 9

**REE** rich execution environment. 10

**RISC** reduced instruction set computing. 29

SGX Software Guard Extensions. 11

**SML** Standard ML. 18

SMM System Management Mode. 15

SMMU system memory management unit. 15

${\bf SMT}$  satisfiability modulo theories. 17

SoC System-on-a-Chip. 29

**TCB** trusted computing base. 5

**TEE** trusted execution environment. 10

**TLB** translation lookaside buffer. 30

**TLS** topl-level specification. 27

**TPM** Trusted Platform Module. 10

# Chapter 1

# Introduction

Encryption works. Properly implemented strong crypto systems are one of the few things that you can rely on. Unfortunately, endpoint security is so terrifically weak that NSA can frequently find ways around it.

Edward Snowden

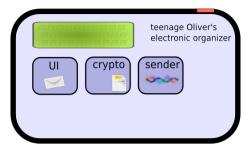

In the 1990s I possessed an electronic organizer for teenagers. One of its features was the ability to send messages to other such organizers via infra-red transmission. According to the manufacturer, messages would be secret and only visible to me and the person I had a crush on. Back then I was not interested in security yet. Besides, none of the persons I had a crush on was an owner of such an organizer. Twenty years later I wonder how the manufacturer actually implemented its security promise. In good faith in the manufacturer, I assume they used the strongest encryption available. But as pointed out by Snowden in the quote above or by Kocher in [107], cryptography is less of a concern than the security of the computing devices on which this cryptography is processed. My electronic organizer at least ran some user interface, the encryption service, and the infra-red network driver, as shown in Figure 1.1. One might think that the encryption service is the only process relevant for security. However, the user interface had access to my love letter in clear text and possibly could have circumvented the encryption by sending the message to the infra-red module directly. Also, the network driver – maybe third party code – might have contained bugs or backdoors that somehow would read the love letter from the memory of the other modules. In the end, it is possible that confidentiality depended on all three processes. In technical terms, the *trusted* computing base (TCB) of my organizer might have included all of them.

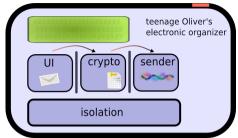

If we are more optimistic, the electronic organizer might have contained some isolation mechanism (see Figure 1.2), that made sure that the modules were sepa-

Figure 1.1: The electronic organizer with some of the software modules executing alongside each other.

Figure 1.2: The electronic organizer with an isolation mechanism, separating the modules.

rated from each other and could not access each other's memory, except for some dedicated and controlled inter-process communication. With working isolation and the right policies in place, the TCB would then only have contained the encryption service and the isolation mechanism itself. Even if both user interface and network module were corrupted, my messages would always be encrypted before leaving the organizer.

For teenagers nowadays, life is even harder than it was for me back then. Leaving aside the many possible non-technical reasons, this is because their electronic organizers – commonly called smartphones – do not only run code from the manufacturer. Smartphones are connected to the Internet and allow the execution of third party programs. It is no longer only erroneous code that can threaten security, entire programs might be developed with malicious intents. This applies not solely to smartphones, but to many other connected devices, as well. Isolation is needed to protect assets from such malware. If attacks still succeed, isolation can help to limit the damage. And as we have seen above, isolation allows to reduce the TCB.

But in turn, a reduced TCB makes it also easier to increase confidence in the isolation. The smaller the isolation mechanism in my electronic organizer, the more feasible it was for the manufacturer to inspect the mechanism and clear it from bugs. To develop that line of thought a little further, it is worthwhile noticing that isolation has been a key feature of most computing systems for a long time. In fact, one of the tasks of an operating system is to allow the parallel or interleaved execution of several processes and to provide isolation by making sure that the processes do not interfere with each other outside regulated inter-process communication. However, many operating systems are vulnerable to attacks that threaten this isolation. A recent example that was covered broadly in media comprises three iOS vulnerabilities that together allow an attacker to silently install sophisticated surveillance software on the victim's phone when the victim clicks on a specific link [28]. Many more vulnerabilities – also for other systems – were reported in the past. For performance and other reasons the design of most commodity operating systems is monolithic, leading to a large TCB. Assuming a constant error density, a larger code base leads to a higher number of errors. Furthermore, it increases the costs for inspection. In contrast, the analysis of isolation mechanisms with smaller and less complex implementations is easier. This is true for both manual inspection and computer-aided formal verification, that is, the generation of mathematical proofs on the security of a system.

Often such analysis focuses only on the isolating software. However, isolation depends on hardware, as well. Some of a system's hardware was built to enable isolation, such as memory protection units or virtualization extensions. Other hardware can threaten isolation, such as peripherals with direct memory access. It is important to consider these influences when designing and verifying isolation solutions, even more since the role of hardware for isolation is increasing. Similarly, it is crucial to keep in mind that the software responsible for isolation is not the only software on the system. Other software such as arbitrary user programs might compromise isolation if the underlying hardware platform is misconfigured or misdesigned. Furthermore, there might be software executing before the isolation software, potentially preventing isolation from ever being established.

The purpose of this thesis is to improve assurance in respect to such aspects – system aspects which constitute the environment that isolation software executes in. We are particularly interested in the context of virtualization as enabler for isolation, but many results are applicable to other system software, as well. While the thesis cannot address all open challenges, it attempts to contribute towards the ideal of pervasive platform security for general purpose systems. To that end, the following challenges are addressed:

- How can we analyze instruction set architectures to learn about possible information flows that can occur during unprivileged execution? Verifying isolation properties of the processor is more than just obtaining assurance of its security. It is also about learning what system components need to be banked, cleared, or restored on context switches. And finally, such analysis yields information on how to configure the system, such that user processes are sufficiently restricted.

- How can we maintain isolation when peripherals execute in parallel with the CPU and have direct access to the memory? A complete exclusion of such peripherals is not a practical option in most cases. Virtualization software needs to provide its guests with access to those devices, however, in a controlled manner. If no dedicated hardware support (such as an IOMMU, see Section 2.1.3) is available, the virtualization software needs to function as a proxy, check policies, and possibly multiplex accesses to peripherals. System models need to be adopted to enable reasoning on the partitioning implemented by the composed computing system.

• How do we guarantee the launch of uncompromised isolation software in previously unprotected software stacks without completely rebooting the system?

The thesis is comprised of both publications that focus on formal verification and publications that focus on the design of platform security solutions. While the work presented in this thesis was performed in projects with emphasis on embedded systems, many results are general and can be applied to strengthen the security of other platforms.

**Thesis Outline** Following this introduction, a background section establishes the main concepts within platform security and formal verification that are relevant for this thesis. Furthermore, the main challenges and related work are discussed. In Chapter 3 the contributions of the thesis are first described on a high level and then on a per-paper basis, together with declarations of the individual contributions of the author. For completeness, the author's publications outside this thesis are listed at the end of the chapter. Chapter 4 concludes the first part of the thesis with a summary and a discussion of possible future work. Thereafter, six of the author's paper are included. Some of them contain minor extensions to the original publications. Otherwise the papers are included as originally published, but adopted to the style format of this thesis. A common reference list for all included papers and introductory part of the thesis can be found at the end.

# Chapter 2

# Background

## 2.1 Platform Security

IT security can be divided into a number of subfields, including for instance cryptography or network security. This thesis focuses on the subfield of platform security. The goal of platform security is to secure computing platforms, ranging from small sensor nodes over smartphones and personal computers to industrial servers. The main ambition is to protect the integrity and confidentiality of software, credentials, and other data, while they reside on the computing platform. Threats to those security properties can be of both physical and logical nature. While physical attacks on the platforms have high impact potential, they are less likely in most scenarios. Instead, this thesis discusses protection from threats that allow malicious software (called *malware*) to infiltrate the victim's system via storage media or remotely via a network.

Two concepts are vital for protection from malware: *isolation* between potentially malicious software and assets to protect, and the establishment of *trust* in integrity and authenticity. Processes should not be allowed to influence other processes or access their data, except for explicit communication. Besides protecting processes from each other, the isolation enabler also needs to protect itself from undesired modification. Once a software stack with such isolation properties is developed, the second challenge is to provide the users or third parties with assurance that the system they interact with actually is the system they assume, that is, that they trust. This trust establishment is sometimes also called *attestation*. *Remote attestation* is the attestation of a system's state to a remote party, for instance over the network.

Isolation can be achieved in many ways. Software aiming to isolate processes (e.g., an operating system (OS) isolating applications) could potentially interpret the processes line by line and dynamically check each instruction against policies before executing it. Alternatively, it could statically check that code follows the desired policy before handing over execution to the corresponding processes. However, while the first option is prohibitive in terms of processing time, the second is hard to achieve, due to obstacles such as self-modifying code. In practice, system software therefore relies on hardware support to establish isolation. Such support allows direct execution of untrusted code on the CPU while still maintaining isolation. Most prominently, memory protection units (MPUs) and memory management units (MMUs) allow privileged code to set selected regions of the main memory inaccessible throughout the execution of a process. Memory protection policies can restrict readability, writability, executability, or combinations thereof. Processors usually support the execution on different privilege levels to make sure that applications cannot change memory protection or other privileged settings, while operating system kernels can. Transitions between privilege levels (or operation modes) follow well-defined schemes, that – for instance – enforce the execution of specific code (called *handlers*) on entrance into a privileged mode. The hardware can be configured to invoke the kernel on certain events (*exceptions*) such as interrupts from a peripheral or when unprivileged software attempts to access restricted memory.

#### 2.1.1 Trusted Execution Environments

Due to the size and complexity of operating systems, OS developers often fail in keeping code free from vulnerabilities that threaten the isolation of user processes. Therefore, several initiatives attempt to enhance platforms with additional isolation that is stronger than the one provided by most operating systems. This isolation can then be used to protect select code and data, even if the OS is compromised. Environments providing such integrity- and confidentiality-protected execution are often referred to as *trusted execution environments (TEEs)*. <sup>1</sup> They operate along-side the *rich execution environment (REE)* – including the commodity OS and its applications – but subject to some (hardware) separation [121] and usually offering services to the REE [136].

Some TEEs are provided by the processor designers, such as by ARM's Trust-Zone extension [11]. TrustZone's TEE is called *Secure World* and manages its own virtual MMU and own vector table [59]. An additional address bit allows to assign both memory regions and peripherals exclusively to the Secure World. However, the Secure World always has access to the REE (or *Normal World*).

Trusted computing [174] is another enabler for TEEs. In trusted computing, software that is loading new software uses special CPU instructions to calculate integrity measurements of the loaded binaries. Those measurements are computed with the help of hash functions and reported to a special cryptographic hardware component – the *Trusted Platform Module (TPM)* – before execution is handed over to the loaded software. Measurements can be computed incrementally while

<sup>&</sup>lt;sup>1</sup>Note that the term TEE is overloaded in the security community. The definitions which we follow in this thesis only require isolated processing and memory. However, there are other definitions of TEEs that have stricter requirements and include, for example, boot integrity, secure storage, and device identification/authentication [63].

building up the software stack or only for a single binary block to load, sometimes called *late launch* [100, 82, 1, 116]. In the incremental case, the reported measurements help to attest the integrity of the entire software stack as long as all reporting modules are trusted. In late launch, hardware guarantees that the TPM-reported binary actually has received control at some point. Note that this attestation of integrity is not the same as integrity enforcement – it is still possible that manipulated binaries are loaded and executed. However, in that case attestation will fail. Since it is possible to make access to credentials subject to attested integrity, attacks on the software's integrity would be rendered useless in some scenarios. In practice, credentials are either provided from a remote machine after integrity has been attested or – with *sealed storage* – revealed by special hardware.

When those methods are used correctly, they can guarantee the integrity of launched software and indirectly the integrity and confidentiality of data. However, by itself this guarantee only holds as long as the launched software is the only one executing on the machine. When handing over control or when executing on multicore systems the software needs to take additional measures to maintain isolation, for instance through memory protection or clearing state on context switches.

To minimize such overhead - and in consequence the code to rely on - Intel introduced its *Software Guard Extensions (SGX)* [8, 119, 94, 118, 183]. TEEs based on SGX are called *enclaves* and it is the processor that ensures integrity and confidentiality once code and data are loaded into such an enclave. Throughout the execution of an enclave, software executing alongside cannot interfere with or learn about the enclave's execution, apart from explicit communication and side channels such as page faults (cf. [184]). Since enclave code is not protected before the enclave is loaded or after it is destroyed, remote attestation and sealed storage are employed to maintain protection of integrity and confidentiality at those times. For low-end embedded systems such as sensor nodes, Sancus [131] provides similar protection to that of SGX.

To fully understand the benefit of TEEs, the concept of a *trusted computing* base (TCB) is essential. The TCB of a system is "a small amount of software and hardware that security depends on and that we distinguish from a much larger amount that can misbehave without affecting security" [109, page 270]. While other definitions (e.g., [110, page 112, glossary]) understand the TCB as a set of dedicated protection mechanisms, in this thesis TCB is to be understood as the totality of any software or hardware that actually has the capability and privileges (but not necessarily the intended functionality) to compromise security. The user thus needs to trust the TCB. Trust in that sense does not distinguish between malicious intentions and exploitable errors. For the user of a platform it does not really matter if the platform's operating system was written to leak/manipulate the user's data or if the operating system is "only" vulnerable enough to allow an attacker in the form of a malicious application or remote party to cause damage. Both cases are clearly undesirable. Since complex (sub-)systems are hard to secure, one of the main paradigms of security research has therefore become to minimize this trusted computing base. And that is in the end what TEEs are developed

for. It is not the case that operating systems *in principle* could not isolate critical from untrusted applications. But isolation is not their sole task and – especially monolithic – operating systems often have a larger TCB than TEEs. This is clearly a disadvantage when it comes to exhaustive examination.

We next turn to virtualization, the enabler for TEEs that we focus on in this thesis.

### 2.1.2 Virtualization

Virtualization provides to software a system view of interfaces and resources that differs from the actual (physical) interfaces and resources of the system [164]. Virtualization can be used for compatibility reasons, for resource sharing, or for isolation. One of the most common forms of virtualization - process virtualization - is performed by operating systems to provide processes with a standard interface where context switches and variations in physical memory layout are transparent. In contrast, in system virtualization [164] it is the operating system could be hosted by another one. Alternatively, operating systems can execute side-by-side on a single physical device without another operating system hosting them. This latter form is called type-1 [79, section 2.1] or bare metal virtualization. We refer to the software that provides this virtualization as a virtual machine monitor or hypervisor and to the software systems executing upon their virtualized interface as virtual machines or guests.

A type-1 hypervisor might attempt to provide its guests with a view that is identical to the physical system, modulo the extent of available resources like memory, cores, or time. This form is known as *full virtualization* and makes it transparent to the guest that it is executing in a virtualized environment. In contrast, *paravirtualization* refers to the modification of guests in order to function in the virtualized environment. Typically, such paravirtualized guests would issue system calls invoking the hypervisor for privileged functionality, so-called *hypercalls*. Alternatively, a hypervisor can be invoked on exceptions, such as interrupts, data or prefetch aborts, or a guest's attempt of executing a privileged instruction. Such *trapping* is used in both paravirtualization and full virtualization. In the latter case, the hypervisor consequently *emulates* the functionality that the guest failed to execute.

While paravirtualization can be done with the same hardware enablers that operating systems usually use, full virtualization can be hard or even impossible without additional hardware support. The minimum requirement for full virtualization is that all privileged operations trap into the hypervisor when attempted by guests. However, since guests usually maintain their own isolation hierarchy (between OS kernel and applications), a hypervisor would need to emulate hardware functionality such as system calls and memory management, if it is intended to provide the guest with this internal separation. Since that can be a tedious task, modern hardware platforms provide virtualization support such as multiple privilege rings or a 2-stage-MMU. A 2-stage-MMU allows the guest OS kernel to directly

#### 2.1. PLATFORM SECURITY

define an address translation from virtual addresses to intermediate addresses and the hypervisor to define the translation between those intermediate addresses and physical memory.

Isolation in the context of virtualization is fulfilled when guests are not able to learn about fellow-guests or influence them. Sometimes, one wants to relax this interpretation and support functionality like inter-guest communication. It can still be meaningful to speak about isolation then, given that guests cannot influence each other in any other way than via a controlled well-defined communication channel.

Separation kernels are similar to hypervisors and the two terms are often used without sharp distinction. Rushby introduced separation kernels as software that mimics a distributed environment, with guest processes executing separately from each other except for explicit communication [144]. The (security) term "separation kernel" is more common for kernels that focus on isolation and whose guest processes do not necessarily have operating systems. In contrast, the term "hypervisor" often refers to virtualization software with more virtualization functionality and complex guest systems. For instance, a hypervisor would typically apply memory translation instead of pure memory protection with a 1-to-1 mapping. Because of the overlapping terminology, this thesis often employs the term "hypervisor" for both types of system software.

#### 2.1.3 System Aspects of Isolation

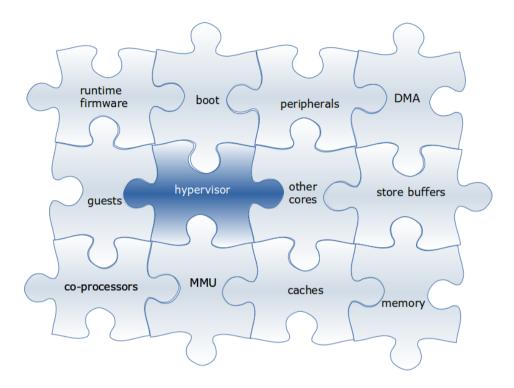

The security of a virtualized platform does not solely depend on the linear execution of hypervisor code. Actors coexisting with hypervisor threads (Figure 2.1) influence the system, among them:

- code that executes before the hypervisor, that is, boot code.

- code that executes in between two hypervisor handlers on the same core, that is, runtime firmware (e.g., for power management) or guest code. Firmware code is often unknown. Guest code can be any arbitrary code, only limited by the privilege management of the instruction set architecture (ISA).

- code on other cores. This code executes in parallel and can be another hypervisor thread, a guest, or firmware. Some of the resources accessed by a core are exclusive to that core, while other resources are shared between the cores, creating race conditions and data leakage, for instance.

- peripherals operating in parallel.

- system components that are executing on behalf of the hypervisor or the other actors above, but do so in parallel and with delays, that is, without predictable execution sequences. That is the case for co-processors, but also for the entire memory subsystem, including store buffers, caches, and memory management.

Figure 2.1: System security is influenced by many actors.

It is essential to understand how the above actors can change the system, what information they can access, and under which circumstances this happens. This knowledge allows for the correct system configuration and implementation of context switches and other hypervisor operations. However, this matter is not trivial and the past has shown that many of the coexisting actors in the system can set security at risk. This subsection surveys some of the known issues.

Much complexity is introduced through peripheral devices. On some architectures, the programmer has access to specific commands to communicate with peripherals. On other architectures like ARM, peripheral devices are mostly memory mapped, i.e., their ports are accessible via standard load and store instructions. From the programmer's perspective, memory mapped devices do not differ from actual memory. The only attribute that distinguishes them from memory is their physical address. Therefore, the MMU can be used to constrain which device ports the CPU has access to. However, some devices have *direct memory access* (*DMA*) and can read from or write to both physical memory and other devices on the bus. If untrusted code has access to DMA controllers, the controllers can be programmed to circumvent memory isolation. Wojtczuk demonstrates on x86 how only come from software.

a manipulated driver for a network interface controller (NIC) or hard disk drive (HDD) can use DMA to modify code and data of a Xen 3.x hypervisor from the (relatively privileged) dom0 guest domain [181]. DMA attacks have also been used to develop stealthy keyloggers, undetectable by the host [169]. *Input/output memory management units (IOMMUs)*, also called *system memory management units (SMMUs)* in ARM terminology, are one way to counteract DMA attacks. They can be programmed by system software to constrain the address space accessible by adjacent peripherals. However, many embedded devices do not include an IOMMU. Alternative ways of protection against DMA attacks are discussed in Chapter E. A special form of DMA attacks is based on the *FireWire* technology implemented via the Open Host Controller Interface (OHCI). As shown in [32], the interface provides DMA to external peripherals without the involvement of system software. Therefore, malicious external peripherals can compromise the system even without previously installed malware. There are countermeasures to those attacks, for instance OHCI filters, but FireWire attacks still demonstrate that threats do not

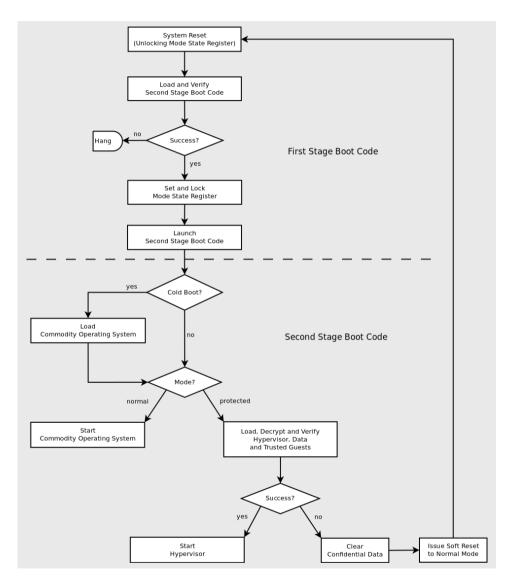

Before the hypervisor has even a chance of setting up the machine to protect itself, firmware – such as the basic input/output system (BIOS) – and boot code are executing. We need to trust this code to load the hypervisor as expected. Secure boot schemes (e.g., as in [127]) use read-only memory and cryptographic means to guarantee the integrity of the hypervisor and guests. Trusted boot schemes also attest this integrity to the user or remote parties. These schemes can help to protect, for instance, against manipulations on the storage device that contains the hypervisor code before boot. However, we still need to rely on the correctness of the boot code sequence itself. Unfortunately, BIOS software is not standardized and rarely updated, and many BIOS systems are known to have vulnerabilities [108]. Even worse, firmware is not only a concern at boot time, but remains active afterwards. A well-known example of this is the System Management Mode (SMM) on Intel's x86 machines. The SMM is invoked for power management, for instance, and executes without restrictions on memory or I/O. Furthermore, it has access to the context stored by the CPU when entering SMM. It is thus quite attractive for an attacker to operate in SMM. The memory that contains the SMM handler code is supposed to be protected, but some attacks have managed to overwrite it [62]. These attacks already require at least administrator privileges, but allow the attacker to become even more powerful [62] or to install a stealthy rootkit [64, 154] that the operating system (or hypervisor) cannot detect. While SMM is specific to x86, similar issues might exist on other platforms. Also on ARM, firmware code executes during and after boot and in a powerful setting (e.g., in the Secure World of TrustZone). As pointed out in Section 2.1.1, TEEs are supposed to reduce the amount of code we need to trust. At the same time, these examples show that TEEs can reduce the ability for users to gain trust when the TEEs hide third-party code from inspection.

Side-channels are a more subtle attack vector than the ones discussed above. However, it has been repeatedly shown that they allow the extraction of cryptographic keys, for example. Furthermore, they are hard to avoid and exist in various forms. Among the most important representatives are cache channels, which can be both timing-based or purely logical [135, 143, 99, 185, 83]. Physical side-channels include the analysis of power, electromagnetic patterns, or acoustic emanations. For instance, Genkin et al. demonstrated that inexpensive equipment can extract keys over the electromagnetic channel in a few seconds from a distance of a half meter [76].

The purpose of this subsection is to give an intuition of the complexity of modern systems. There are more components that would deserve attention, for instance debug registers, but a complete survey is out of scope of this thesis. The ambition of this thesis is to improve assurance for a few pieces of the complex puzzle just described. In particular, the included results focus on the security during boot, during user mode execution, and in the context of DMA-devices.

### 2.2 Formal Verification

Assurance of the correctness of soft- or hardware has traditionally been derived from testing and manual inspection. However, those methods are far from complete. To increase assurance, a range of machinery has been developed to actually prove correctness. While the assurance obtained from such proofs can still vary, all approaches share the idea of creating mathematical models of the systems to analyze and subsequently derive or confirm - also mathematically - formal properties. By *formal* we mean that those properties are expressed as statements in some logic. Consequently, those methods are referred to as *formal methods* or *formal verification*.

#### 2.2.1 Representatives of Formal Methods

Next, we survey the most prominent representatives. Note that although we attempt to categorize the different approaches, a sharp separation is not always meaningful.

**Model Checking** In model checking, the system to verify is modeled as state transition system and automated graph search algorithms check if the given specification holds of the system's state graph [65]. The specification is usually formulated as a temporal property, thus expressing behaviors such as "it is always (i.e., in every state) true that X" or "whenever Y occurs, eventually Z will become true". On violations of the specification, the model checking tool exhibits a counterexample. The advantages of model checking are the automation and user-friendliness. On the downside, the exhaustive exploration of the state graph is expensive (*state space explosion*). This practically prohibits detailed system models (e.g., where a machine's memory is modeled completely as a huge array of words). The model designer thus has to abstract the state, with the risk of missing relevant behavior.

#### 2.2. FORMAL VERIFICATION

**SAT Solving** Propositional logic formulas can be transformed into an equivalent formula in conjunctive normal form (CNF), that is, a conjunction of clauses that are in turn disjunctions of possibly negated variables [97, chapter 1.5]. Determining whether or not such a formula is satisfiable is known as the *Boolean satisfiability problem (SAT)*, which is decidable, but in general NP-complete [48]. However, in practice *SAT solvers* can decide the satisfiability of many formulas in acceptable time. Generalizing the concept of SAT solving, solvers for *satisfiability modulo theories (SMT)* (e.g., [56]) allow to include domain-specific theorems (e.g., on integer arithmetic) into the reasoning. SAT solvers can be directly applied for reasoning on state transition systems [159] or for automatically discharging sub-obligations in other proof tools.

Static Automated Program Verification Static verification of functional and safety properties for software can be automated to a large extent. The "model" is the program code itself, as source code, in an intermediate format (e.g., Java bytecode), or as binary. The specification is usually given as a contract of preand postconditions on code blocks. In addition to those assertions, the user can typically provide intermediate assertions such as loop invariants to facilitate the reasoning. The most prominent notation is based on Hoare-triples [93] of the form  $\{P\}C\{Q\}$  expressing that if precondition P holds then program code C will progress the program to a state where Q is true. Total correctness additionally requires termination of C, while partial correctness only assures Q under the condition that C terminates. Axioms and proof rules allow to derive and combine such triples based on the operational semantics of the code language. They describe how preand postconditions relate in the context of for example assignments, sequential composition, or branches. Starting from the desired postcondition, those rules allow to automatically infer the weakest precondition. Alternatively, one can start from a known precondition and infer the strongest postcondition. Along the process, proof obligations are accumulated. Their conjunction - the verification condition - is a first order formula that can be verified by an SMT solver in many cases. Loops and less simple relations on arithmetics and data structures might require additional user interaction. Examples of static code verification tools are the Binary Analysis Platform (BAP) [43] for binary code and VCC for concurrent C [47].

**Protocol Verification** Outside of platform security, formal verification is for example used to verify the security of network protocols that make use of cryptographic principles. Given a model for the protocol and the attacker's behavior, they check what an attacker can achieve in the protocol. Examples of protocol verification tools are ProVerif [37, 38] and AVISPA [177].

**Interactive Theorem Proving** Despite the name, an *interactive theorem prover* is more of a proof checker than a proof generator, even though more and more automation finds its way into modern theorem provers. The core principle of an

interactive theorem prover is that propositions can be stated in some specific logic and that inference rules allow to transform assured propositions (such as axioms) into new assured propositions. The inference rules can be both of a basic kind or derived complex rules. Among the most prominent theorem provers are HOL4 [95, 81], Isabelle [101], and Coq [33]. They all have some form of meta language that allows to operate on *terms*, i.e., expressions in the logic. For HOL4 that meta language is Standard ML (SML), a widely-used general-purpose functional language. Logical propositions in HOL4 are simply terms of Boolean type. It is important to point out that there is a difference between SML types and HOL4 types. When we say "a term of Boolean type", then we actually mean that the HOL4 type of the term is Boolean, while the SML type is term with bool as a type parameter. Proven propositions along with their premises are represented in an abstract SML-type for *theorems*. This type does not have primitive constructors. Therefore, users can only construct objects of the theorem type with sound primitive inference operations  $^{2}$  [132]. SML allows to combine those inference operations to arbitrarily complex operations on theorems. Below we discuss the most common ones. Rules transform theorems to new theorems. For instance, the rule SYM would turn 1+2=3 into 3=1+2. Conversions take as input a term and turn it into a theorem that states the equivalence of that term to some other term computed by the conversion. For example, a conversion could generate the theorem 1+2=2+1from the input 1+2. Instead of reasoning from known theorems forwards to desired theorems, the opposite is possible as well and is called *backward reasoning*. A proof goal is reduced to one or several subgoals including premises, which is then repeated recursively, generating a proof tree (or *proof stack*). This procedure is usually performed in a depth-first manner, moving upwards whenever a leaf node can be finished off completely. The proof stack is managed by a *proof manager*, that also comes with some sort of user interface when used interactively. Reductions are based on so-called *tactics*, functions from a  $goal^3$  to a list of subgoals and a justification function. The justification function allows the deduction of the desired theorem from the theorems that would result from the subgoals. Functions that transform tactics are called *tacticals*.

Even though the most common use of HOL4 is to do backward reasoning with standard tactics, HOL4 really allows to "program" proofs more freely. Therefore, rather than understanding HOL4 reasoning as the instantiation of a fixed proof structure, it should be seen more generally as theorem processing. This allows for proof tools as demonstrated in Chapters B and C. Their development involves algorithm design and programming, just as in the development of arithmetic or graph tools. Instead of numbers and graphs, however, the basic operations are

$<sup>^2</sup> Strictly speaking, HOL4 allows to construct arbitrary theorems even without proof. However these theorems will be tagged. Tags are propagated and cannot be removed. One way of constructing such theorems is by the application of the <code>mk_oracle</code> command, see <code>https://hol-theorem-prover.org/kananaskis-10-helpdocs/help/Docfiles/HTML/Thm.mk_oracle_thm.html</code>$

<sup>&</sup>lt;sup>3</sup>A goal consists of a term as the proposition to prove and a list of premise terms.

inference rules operating on terms and theorems. Since the inference rules are composed from a small set of basic and sound rules, obtained theorems are sound.

#### 2.2.2 State Transition Systems

In the following, we use the term *machine* as general concept of a computing system - be it a single processor core, a peripheral, or an entire device. A machine has components such as registers, memory, control flags, or a coprocessor, and those components can in turn have subcomponents. The state of a primitive component is the value it currently holds, while the state of a complex component or the entire machine is a structure comprised of the states of all subcomponents. Whether this structure is represented as tuple, record, or some other type, depends on the mathematical model of the system. In deterministic settings, machine progress can be represented by *transition functions* that take a pre-state, possibly along with some parameters, and return a post-state. If non-determinism needs to be modeled, relations between pre- and post-states are a suitable generalization. The models used in this thesis are on instruction set level and most of them do not include non-determinism, since they do not consider timing, concurrency or other behavior whose outcome is hard to predict. Chapter D is an exception and includes a model in which a CPU core executes concurrently with peripheral devices. However, we decided to reflect the unknown effect order from concurrent execution with the help of an uninterpreted oracle function. Our proofs then quantify over all possible orders. This decision allowed us to stay closer to the original CPU model than by switching to transition relations. In the following, we focus on transitions represented by functions. Transitions can be of any granularity, representing one processor instruction, only parts thereof, or entire programs. Sometimes, it is meaningful to fix the granularity. Then we use the term *step* for a transition of the chosen granularity. A step sequence is the chained application of steps, so that the post-state of one step is the pre-state of the next step. A chain of involved states in such step sequence is called *trace*.

The state transition systems most relevant for this thesis are the ISA models by Fox et al. [68, 69, 70]. They are available for ARM, MIPS, x86, and other architectures. The instruction sets are modelled based on official manuals and on the abstraction level of the programmer's view, thus being agnostic to internals like pipelines. The newest models are produced in the domain-specific language L3 [68] and can be exported to SML and HOL4.

#### 2.2.3 Noninterference

In the following we introduce the property of *noninterference* as formulated by Goguen and Meseguer [77, 78] and by Rushby [145, chapter 2]. We first present the general formulation and later instantiate it to be close to the scenarios and models discussed in this thesis.

We assume a state transition system with a set S of states, some actions A (e.g., inputs or commands), and a set O of outputs. Given a pre-state and an action, the system takes a step deterministically,  $step : S \times A \to S$ . However, the free choice of the action might introduce a certain nondeterminism if no further restrictions apply. Extending the step function,  $step^* : S \times A^* \to S$  denotes the execution of multiple steps, inductively defined over a list of actions. We assume the existence of an output function  $out : S \times A \to O$  that takes a state and an action and returns an element of O as the output associated with that action on that state. Let D denote a set of security domains, for instance, {public, secret} or a set with one domain per process. The function  $dom : A \to D$  associates a domain with each action. Furthermore, a security policy defines which domains may influence which other domains. We define a function  $purge : A^* \times D \to A^*$  that takes an action sequence and a domain d and removes all actions from the sequence that belong to a domain that is not allowed to influence (i.e., that is not readable by) d.

Rushby provides an intuition for *information flow* as follows: "information can be said to flow from a domain u to a domain v exactly when actions submitted by domain u cause the behaviour of the system perceived by domain v to be different from that perceived when those actions are not present" [145, chapter 2, page 7]. In that understanding, *noninterference* is the absence of undesired information flow.

**Definition 2.2.1.** Let  $s_0$  be a starting state, possibly subject to some preconditions. Then, we say that *noninterference* holds, if for all action sequences  $\alpha$  and all actions a it is true that

$$\mathtt{out}(\mathtt{step}^*(s_0, \alpha), a) = \mathtt{out}(\mathtt{step}^*(s_0, \mathtt{purge}(\alpha, \mathtt{dom}(a))), a)$$

The domain of action a should not be affected by domains removed through purging.

When showing noninterference for a concrete system, reasoning on sequences of state transitions can be challenging. However, noninterference can be reduced to a set of unwinding conditions on single (pairs of) state transitions, see [145, chapter 2] and [78]. A core ingredient for this reduction are state equivalence classes defined for each domain. If two states are in an equivalence relation  $\sim^d$ , it should be impossible for domain d to distinguish them. It is the task of the verifier to identify a suitable relation, guided by the unwinding conditions of the following theorem [145, theorem 1]:

**Theorem 1.** Noninterference holds if for every domain d there is an equivalence relation  $\sim^d$ , such that these three conditions hold:

- 1. output consistency:  $(d = dom(a)) \land s \sim^d t \Rightarrow out(s, a) = out(t, a)$  (for all states s and t and all actions a)

- 2. local policy compliance:  $s \sim^d \operatorname{step}(s, a)$  for all actions a whose domain  $\operatorname{dom}(a)$  is not allowed to influence d (for all states s)

#### 2.2. FORMAL VERIFICATION

3. step consistency:  $s \sim^d t \Rightarrow \texttt{step}(s, a) \sim^d \texttt{step}(t, a)$  (for all states s and t and actions a).

**Proof sketch:** Consider any domain d, an original trace, its purged version, and any pair of states (one state from each trace), such that the two states are related by  $\sim^d$ . We induct over the original trace. For every step we distinguish two cases. Either the action of that step belongs to a domain that is allowed to influence d. Then this step is also represented in the purged version and step consistency maintains  $\sim^d$ . Or else the action of the step does not belong to a domain that is allowed to influence d. In that case, the step has been purged from the other trace, but local policy compliance guarantees that the relation is still maintained, when we advance only in the original trace. Finally, after any walk on a trace pair we will still be in states related by  $\sim^d$ . From there, output consistency allows us to conclude noninterference [145, chapter 2].

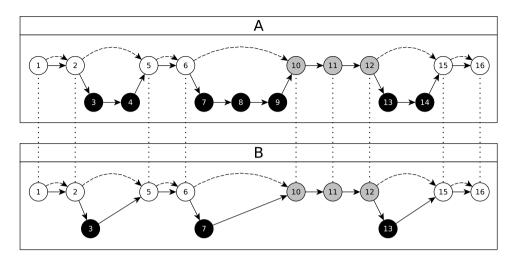

To understand what noninterference means for the scenarios and models in this thesis, we instantiate the above formalism with a system close to the systems analyzed in later chapters. We consider a virtualized single-core machine where two or more guests take turns in execution. A hypervisor handles the context switches, by storing the context of a paused guest to memory and restoring the context when reactivating the guest. For simplicity, we also assume that the hypervisor manages some flag  $flag_g$  for each guest g indicating whether the guest's context is in the context buffer or in the registers of the processor. <sup>4</sup> Context switches are initiated by timer interrupts. For now, we assume that interrupts are the only way to trap to the hypervisor and that guests do not communicate. Guests do not have access to the system time. Intuitively, the established separation implies that a guest cannot learn anything about any other guest. It should not even be able to learn about other guests' existence.

We choose the set D of security domains to contain one domain for the hypervisor and one for each guest (but no further domains). Guest domains are not allowed to be influenced by any other domain. The system models in this thesis mostly represent instruction set architectures, with program code residing in memory, a program counter pointing to the next instruction, the privilege level encoded in some control register, etc. – all included in the modeled state. In such a state transition system, the concept of actions becomes almost superfluous. The state already encodes which actor (i.e., domain – guest or hypervisor) is currently active, and every pre-state only has one possible post-state. The only exceptions to this determinism are interrupt signals. We thus use actions to accommodate interrupts and to make the active domain encoded in the state more explicit for the above formalism. To that end, we choose the set A of actions to equal the set D of domains, instantiate **dom** with the identity mapping, and instantiate **step** :  $S \times D \to S$  with a partial function that takes a state s and a domain d and returns

$<sup>^{4}</sup>$ This information can also be concluded from the remaining machine state, for instance from the program counter and the handler code.

- the progressed machine state after one ISA step, if domain d matches the active actor in s;

- the post-state to s after an interrupt signal, if d is the hypervisor domain, but a guest is active in s.

For simplicity, this instantiation excludes interrupts fired during hypervisor phases, but accommodating them requires minor changes. Note that interrupt steps belong to the hypervisor domain. This modeling decision is motivated by purging reasons. If interrupt actions belonged to guest domains, then execution sequences purged for that guest would end up in privileged mode without any hypervisor or other handler to get the system back into user mode. This would prevent step consistency. The step function is partial, since a step on a machine can only be an interrupt or performed by the active actor/domain. There is no meaningful interpretation of a guest-action when the hypervisor or another guest is executing. A total step function that just idles for such cases would generate some traces that cannot be matched with their purged versions when attempting to show the unwinding conditions. Disallowing some action sequences by choosing a partial step function introduces the additional proof obligation of showing that purging of valid action sequences will always result in valid action sequences again. We omit detailed proofs here. The intuition is that purged sequences will only contain actions associated with one guest, and when starting from user mode with that guest active the system cannot reach a scenario in which this guest is not active any more. <sup>5</sup> As output function we chose a mapping that takes a state s and a domain d and returns a masked version of s, such that:

- if d matches the active actor in s, all components considered readable for d remain as in s, while all unreadable components are overwritten with standard values;

- if d does not match the active actor in s, a state with standard values only will be returned.

Since we assume that the hypervisor can access the entire system, a suitable equivalence relation for its domain is the identity relation. Conditions 1 and 3 follow trivially and so does local policy compliance, since there are no domains that are not allowed to influence (i.e., to be readable by) the hypervisor. The equivalence relations for the guests are less straightforward. Clearly, they should reflect that a guest depends on its own memory, but not on foreign memory. Thus, two states related by  $\sim^g$  would be required to agree on guest g's memory, but would not restrict the states on other guests' memory. Naïvely, we would extend this pattern to other state components, such as registers, requiring two states in  $\sim^g$  to agree on all guest-visible registers and being liberal on all registers invisible to g. This would fulfill

$<sup>^5\</sup>mathrm{Remember}$  that we have assumed that interrupts are the only way to enter privileged execution mode.

output consistency, but leaves local policy compliance unsatisfied, since the guestaccessible registers will be used by the hypervisor and other guests when q is not active. We could relax the relation by removing the restrictions for states in which q is inactive. That is fine for output consistency because of our definition of out. Also, the local policy would be trivially respected in almost all cases. The downside, however, is that we would loose guarantees that we need to re-establish equivalence when the execution returns to q. To maintain these guarantees, we make use of the actual hypervisor design, which involves storing and restoring guest contexts whenever those guests turn inactive or are reactivated. We include the context buffer into the reasoning by letting it take the role of the guest-visible registers when g is inactive. Since it takes the hypervisor several instructions to store or restore the context, we make use of  $flag_q$  to define exactly when the register data of q is considered to be found in the actual registers, (partly) in banked registers, or the context buffer of g. If context storing/restoring is correctly implemented and neither hypervisor nor other guests manipulate the context of g, then phases in which q is inactive will be transparent to q and the unwinding conditions will hold.

From the perspective of g, we can break conditions 2 and 3 further down to five different phases and their proof obligations:

• Execution of g: During the execution of g, the local policy is trivially respected. For step consistency, we need to show  $s \sim^g t \Rightarrow \text{step}(s,g) \sim^g$ step(t,g). This property is often referred to as non-infiltration [90] in this thesis. When g is active, the relation  $\sim^g$  relates states that agree on the observable components. Therefore, non-infiltration expresses that a variation of secret state components will not cause variations of observable components. Definition 2.2.1 of noninterference considers a composed system and an interleaving of several actors/domains. In contrast, non-infiltration can be understood as the local perspective (here of g) on noninterference. That is why in the literature – especially in the information flow analysis of programs – non-infiltration is often directly referred to as noninterference [147] or similar terms such as batch-job noninterference [19]. Chapters B, C, and D follow this convention.

In order to show non-infiltration over the course of several instructions, we need an invariant on possible preconditions to non-infiltration. For instance, it usually has to be shown that g is not able to affect the page tables. Otherwise, it would be able to learn information in the next step and thus break non-infiltration. The integrity property that g cannot manipulate certain machine components is called *non-exfiltration* [90].

• Change of processor mode: In order to reason about privileged execution, several guarantees have to be established when switching the processor's privileged mode. Most importantly, the program counter must be pointing to a well-defined position in an exception handler. That is, guests should not be

able to switch to a privileged execution mode and execute arbitrary code there. Similarly, endianness and instruction set flavour need to be set as expected instead of guest-defined. Interrupts need to be masked. The return address should in fact belong to g. We refer to those properties as *switching properties*.

- Storing/restoring context: With the help of the switching properties we can now reason about the hypervisor code. The central part here is to show that storing and restoring context complies with the local policy (condition 2). Step consistency follows trivially.

- Independent hypervisor execution: For the rest of the hypervisor execution, we essentially have to show that the remaining hypervisor code does not modify the context buffer or memory of guest g.

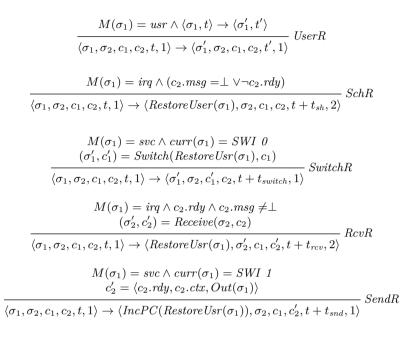

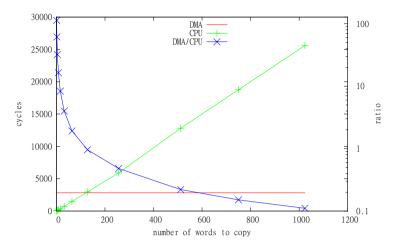

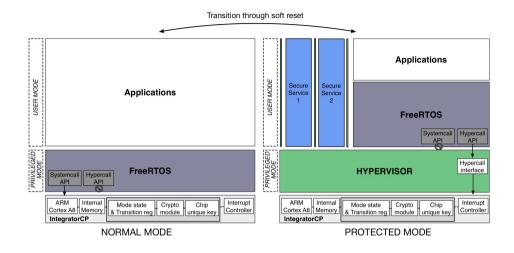

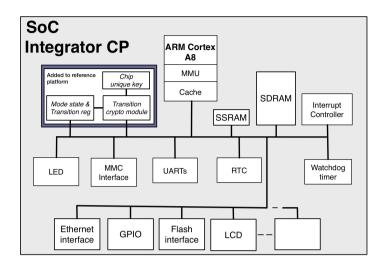

- Execution of other guests: Also the other guests should not modify the context or memory of g in order to guarantee local policy compliance. Furthermore, they must not perform any state modifications that would invalidate the preconditions of the properties above. To that end, non-exfiltration provides all necessary guarantees on the integrity of page tables, hypervisor data and code, and g.